Avionics Databus Solutions

# AXC-FDX-2

2 Port 10/100/1000Mbit/s AFDX®/ARINC664P7 Test, Simulator and Monitor Module for XMC

Data Sheet

www.aim-online.com

# AXC-FDX-2

## **General Features**

The AXC-FDX-2 is AIM's new high performance XMC module offering full function test, simulation, monitoring and analyzer functions for AFDX®/ARINC664P7 (Avionics Full Duplex Switched Ethernet) networks. Versions available for both Airbus and Boeing variants of the ARINC664P7.

The board supports the Boeing ARINC664 extensions for EDE at the hardware interface layer with field proven real time simulation of EDE subscribers to meet all parts and multiple revisions of the EDE specifications. Its unique onboard processing capability, memory resources, customized AFDX® MACs and IRIG-B time code decoder/generator gives AFDX® users a comprehensive feature set for the most demanding AFDX® applications.

The AXC-FDX-2 module provides 2 AFDX® ports being configured as 2 single or 1 dual redundant port each implementing a 10/100/1000Mbit/s full duplex Ethernet interface. Ports can operate concurrently in traffic simulator or receiver/monitor modes with support for AFDX® port related frame statistics. Virtual Link (VL) packet capturing and monitoring features are complimented with powerful triggering and filtering capabilities. An integrated TAP mode enables analyzing network traffic in-line, with all onboard and PBA.pro features between 2 attached Ethernet devices.

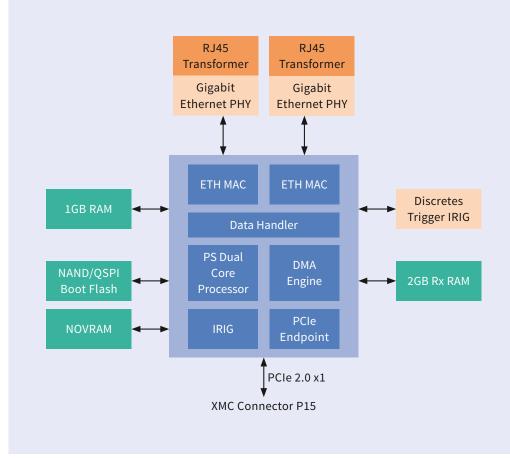

The AXC-FDX-2 uses AIM's field proven Common Core hardware design, utilizes a powerful System on Chip (SoC) system, integrated in a Xilinx ZYNQ® device, including programmable logic and a dual core processor. One processing core is acting as Bus Interface Unit (BIU) processor and the other as the Application Support Processor (ASP). The extensive memory resources onboard allow to implement large receive buffers and complex transmit scenarios onboard.

An AFDX®/ARINC664P7 specific Physical Bus Interface implements 2 full duplex ports for connection to AFDX® networks. The AXC-FDX-2 module is available with the optional PBA.pro analyzer software package for Windows and Linux.

#### AXC-FDX-2 Block Diagram

- 10/100/1000Mbit/s Ethernet compliant Frontend

- Xilinx ZYNQ<sup>®</sup> SoC, including Dual Core Processor

- Designed for Applications such as:

- Test and Verification of End Systems

- Switch Testing

- Monitoring of traffic between End Systems and Switch

- Inter Switch Traffic Analysis

- Multi Stream High Level System Integration

- Programmable Ports Traffic Simulator and Receiver/Monitor Concurrently

- Synchronized Timing across Multiple Modules

- Driver Software for Windows and Linux

## **Traffic Generation**

The AXC-FDX-2 provides real time traffic generation on both ports concurrently. Transmitter operation allows users to fully programme all fields of the AFDX® frame including the Virtual Link Identifier, MAC Source Address, IP Structure, UDP Structure, Payload and Sequence number. Multiple modes of transmit sequencing are supported, these being generic/replay and UDP port oriented shaped transmissions. Users can program payload data with user defined or fixed data. Inserting the time tag in the payload data provides an elegant solution to measure frame transmit delays through the network. Synchronization of transmissions across multiple ports is achieved by using strobe inputs/outputs.

- Programmable Timing and Sequencing of Frames

- Physical Error Injection CRC, Gap, Size, Alignment

- Logical Error Injection on Layers 2, 3, 4

- Timing Error Injection Violation of Bandwidth Allocation Gap (BAG)

- Autonomous Dynamic Data Generation

- UDP Port Simulation with Traffic Shaping

and Sequence Numbering

- Onboard Support for sampling and queuing Ports

## **UDP/VL Receive Mode**

The AXC-FDX-2 module ports can be configured to work in UDP/VL oriented receive mode. In this mode each UDP port has a separate buffer queue. Received frames are stored with frame headers containing time tag and status information. Frame header information can be stored and payload data optionally discarded for the testing of switches and the complete network. With the traffic shaping verification enabled, any violations are reported as errors in related frame headers.

- VL oriented Filtering

- Second Level Filtering on Generic Frame Parameter

- Time Stamping of Received Packets with extended IRIG-B Time Code

- Physical Error Detection, Frame Level CRC, Gap, Size and Alignment

- AFDX<sup>®</sup> Specific Error Detection

- Traffic Shaping Verification

- Verification of MAC, IP and UDP Headers

- VL oriented Integrity Checking

## Chronological Receive Mode (Monitor Mode)

The AXC-FDX-2 module ports can be configured in chronological receive mode to sequentially receive frames and store them in a circular buffer. The payload data can be discarded to optimize the use of the buffer for frame capture and analysis. Powerful filtering, triggering, complex triggering and capture modes allows users to select only the frames, data and errors of interest. Monitor mode also provides activity monitoring and statistics for each VL recorded by the AXC-FDX-2 module. The interface modules report the number of frames received and the number of errors detected globally and in VL orientated format.

- VL orientated Receive and Filtering

- Second Level Filtering on Generic Frame Parameters

- Chronological Monitor with Time Stamping

- Massive onboard Monitor Buffer

- Inter Frame Gap Time Measurements with 40ns Resolution

- Comprehensive Triggering/Filtering/ Capturing

- Programmable Data Capture Modes Trace after Trigger and Recording

- Physical Error Detection CRC, Gap, Size and Alignment

- AFDX<sup>®</sup> specific Error Detection

## TAP Mode

The AXC-FDX-2 can operate in TAP mode in all network speeds. This allows to analyze the network traffic between 2 attached network devices. Inter-Message-Timing will not be changed in this operational mode and network data will not be modified ensuring full operation of attached ports.

## **Application Support Processor**

The Application Support Processor (ASP) is realized using 1 core SoC processing system and provides unique on-module processing functions typically provided by host PC processing systems.

- IP and UDP Layer of the AFDX® Protocol

- Driver Software Execution on the Board

- Dynamic Data Generation

- Loop/Pollution between Rx and Tx Port

- Automatic Test Sequence Generation

- Program using Linux Operating Systems

## IRIG-B Time Code Decoder

An onboard IRIG-B time code decoder and generator allows synchronization of multiple AFDX<sup>®</sup> ports using multiple AXC-FDX-2 modules. Modules can be synchronized using an external IRIG-B time source or the onboard time code generator of 1 module as the reference for accurate correlation of data across multiple AFDX<sup>®</sup> ports.

### **Physical Bus Interface**

The AXC-FDX-2 modules provide 2 AFDX<sup>®</sup> ports which can be used as 2 single channels or as 1 dual redundant channel AFDX<sup>®</sup> specific physical bus interface.

- Customized Media Access Controllers (MAC's) implemented in FPGA (SoC), optimized for AFDX<sup>®</sup>

- 3GByte DDR3 Memory for System, Receiver and Transmitter Buffer

- Physical Interface and Magnetics (COTS)

- 8-Socket Network Interface Connectors RJ45

- Trigger, Strobe and Time Code I/O

Connector

## **Driver Software Support**

The driver software is supplied with the ACC-FDX-2 module. A full functional Application Programming Interface (API) is provided compatible with 32/64-bit Windows and Linux.

Host applications can be written in C/C++. A LabView/VI application interface as well as LabViewRT drivers are provided.

## **Technical Data**

#### System Interface

XMC/PCIe Single Lane, compliant to PCIe V2.0

#### Processors

Dual Core Processing System, integrated in SoC device

#### Memory

1GByte DDR3 Processing System RAM 2GByte DDR3 MAC Receiver RAM

#### Encoder/Decoder

2 AFDX<sup>®</sup> specific Ethernet MAC's, integrated in SoC device;

Inter Frame Gap generation and measurement with 8ns resolution (1000Mbit/s operation)

#### Time Tagging

46-bit absolute IRIG-B time with 100ns resolution;

Inter Frame Gap generation and measurement with 8ns resolution

#### **Physical Bus Interface (PBI)**

2 full duplex AFDX® ports configurable to 1 dual-redundant AFDX® port or to

#### 1 TAP port Connectors

2 x 8 way RJ45 connectors, 1 per AFDX<sup>®</sup> port; 1 x 15 way D-Sub connector (female) for time code, discrete I/O and trigger I/O; XMC connector P15 for single lane 5Gb/s

## PCI Express Bus

Dimensions

Single width XMC standard: 149mm x 74mm

## **Power Consumption**

Typical 4.7W (10/100Mbit/s) / 5.5W (1000Mbit/s) (operating)

#### **Operating Temp. Range**

Standard: 0°C to +55°C ambient Extended: -20°C to +75°C ambient on request

## **Ordering Information**

#### AXC-FDX-2

2 Port, 10/100/1000Mbit/s AFDX®/ARINC664P7 XMC Module: Traffic Simulator, Receiver and Chronological Monitor, Integrated Tap Mode, IRIG-B Time Decoder, 3GB DDR3 RAM Includes Driver Software for Windows, LabVIEW VI's, LabVIEW RT, Linux, VxWorks

#### AXC-FDX-2-G

2 Port, 10/100/1000Mbit/s AFDX®/ARINC664P7 XMC Module: Generic TX/RX Function Only, Integrated Tap Mode, IRIG-B Time Decoder, 3GB DDR3 RAM Includes Driver Software for Windows, LabVIEW VI's, LabVIEW RT, Linux, VxWorks

#### AXC-FDX-2-S

2 Port, 10/100/1000Mbit/s AFDX®/ARINC664P7 XMC Module: Simulator TX/RX Function Only, Integrated Tap Mode, IRIG-B Time Decoder, 3GB DDR3 RAM Includes Driver Software for Windows, LabVIEW VI's, LabVIEW RT, Linux, VxWorks

#### Storage Temp. Range

-40°C to +85°C ambient Humidity 0 to 95% non-condensing

#### AXC-FDX-2B

2 Port, 10/100/1000Mbit/s AFDX®/ARINC664P7 XMC Module: Traffic Simulator, Receiver and Chronological Monitor, Integrated Tap Mode, IRIG-B Time Decoder, 3GB DDR3 RAM Including Boeing EDE Specific Extensions Includes Driver Software for Windows, LabVIEW VI's, LabVIEW RT, Linux, VxWorks

#### AXC-FDX-2B-G

2 Port, 10/100/1000Mbit/s AFDX®/ARINC664P7 XMC Module: Generic TX/RX Function Only, Integrated Tap Mode, IRIG-B Time Decoder, 3GB DDR3 RAM Including Boeing EDE Specific Extensions Includes Driver Software for Windows, LabVIEW VI's, LabVIEW RT, Linux, VxWorks

#### AXC-FDX-2B-S

2 Port, 10/100/1000Mbit/s AFDX®/ARINC664P7 XMC Module: Simulator TX/RX Function Only, Integrated Tap Mode, IRIG-B Time Decoder, 3GB DDR3 RAM Including Boeing EDE Specific Extensions Includes Driver Software for Windows, LabVIEW VI's, LabVIEW RT, Linux, VxWorks

Versions available for both Airbus and Boeing variants of the ARINC664P7

\* AFDX® is a registered trademark of Airbus

#### AIM Office Contacts:

#### AIM GmbH

Sasbacher Str. 2 D-79111 Freiburg / Germany Phone +49 (0)761 4 52 29-0 Fax +49 (0)761 4 52 29-33 sales@aim-online.com

### AIM GmbH – Munich Sales Office

Terofalstr. 23a D-80689 München / Germany Phone +49 (0)89 70 92 92-92 Fax +49 (0)89 70 92 92-94 salesgermany@aim-online.com

#### AIM UK Office

Cressex Enterprise Centre, Lincoln Rd. High Wycombe, Bucks. HP12 3RB / UK Phone +44 (0)1494-446844 Fax +44 (0)1494-449324 salesuk@aim-online.com

#### AIM USA LLC

Seven Neshaminy Interplex Suite 211 Trevose, PA 19053 Phone 267-982-2600 Fax 215-645-1580 salesusa@aim-online.com

© AIM 2018 Specification AXC-FDX-2\_09Apr2018 to change wi

Specifications are subject to change without notice.